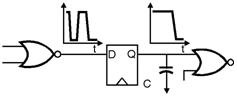

We know how to optimize the power consumption of an isolated logic gate. When designing logic networks, one way to reduce power consumption is to capacitance driven by the gate. However, since the gate consumes almost no power when quiescent, the most effective way to reduce its power consumption is to make it change its output as few times possible. If there is no change in output value the gate is not required. The logic circuit to reduce the number of unnecessary changes to gates output can be designed. To eliminate the glitching the method for power reduction can be used. Glitch reduction may be used in sequential systems. To stop the propa¬gation of glitches, Sequential machines are incorporated with registers. In sequential timing optimizations is considered as retiming. Figure below shows the flip-flops used to reduce power consump¬tion. A flip-flop is connected after the logic with high signal transition probabilities. For repeating the timing, extra levels of registers are added. Adding registers are important when there are more glitch-producing segments are present. However, the number of cycles required to compute the machine outputs should be compatible.

Fig_Power Optimization