- Design-Validation

- EMI-Immune-Design

- IO-Architectures-and-Pad-Design

- Off-Chip-Connections

- One-Phase-System

- Two-Phase-System

Challenges to SOC Designs:

There are several new challenges to SOC designs :

Design Flow of SOC Design :

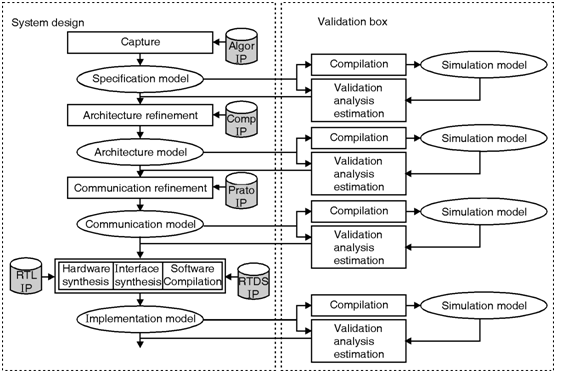

The system on chip design starts with a model which is a functional and free from implementation details. The design focuses on capturing the algorithmic behavior and allows a functional validation of the description. Architecture information can be added in the design during architecture development. In this step processing elements are inserted into the system and functional behaviors are mapped to them. The processing elements are the components are normally generic processors, DSPs and hardware peripherals. Once the architecture is developed, the architecture model captures the decisions created in the designs. This model takes only computing time into account and the communication between the processing elements will be carried out in zero time. The scheduling ranges from a static scheduling to dynamic scheduling which requires busses and protocols. The last step is the synthesis. In synthesis RTL code netlist is created for the hardware. Further, mapping and scheduling is done.

Fig_SOC Designs

Fig_SOC Designs