Home > VHDL > Arithmetic Circuits > Full adder

library IEEE;

use IEEE.std_logic_1164.all;

entity adder is

port (a : in std_logic;

b : in std_logic;

cin : in std_logic;

sum : out std_logic;

cout : out std_logic);

end adder;

architecture rtl of adder is

begin

sum <= (a xor b) xor cin;

cout <= (a and b) or (cin and a) or (cin and b);

end rtl;

2) Full Adder using

Component Instantiation Statements :

library IEEE;

use IEEE.std_logic_1164.all;

use work.gates.all;

entity adder is

port (a : in std_logic;

b : in std_logic;

cin : in std_logic;

sum : out std_logic;

cout : out std_logic);

end adder;

architecture structural of adder is

signal xor1_out, and1_out, and2_out, or1_out : std_logic;

begin

xor1: xorg port map(in1 => a, in2 => b, out1 => xor1_out);

xor2: xorg port map(in1 => xor1_out, in2 => cin, out1 => sum);

and1: andg port map(in1 => a, in2 => b, out1 => and1_out);

or1: org port map(in1 => a, in2 => b, out1 => or1_out);

and2: andg port map(in1 => cin, in2 => or1_out, out1 => and2_out);

or2: org port map(in1 => and1_out, in2 => and2_out, out1 => cout);

end structural;

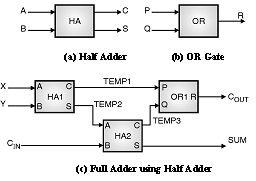

3) VHDL Code for

"Full Adder" declaring "Half Adder" as Component :

(a)Half Adder (b) OR Gate

(c) Full Adder using Half Adder

(a)Half Adder (b) OR Gate

(c) Full Adder using Half Adder

library IEEE;

use IEEE.std_logic_1164.all;

entity FA is

port (X,Y,CIN : in std_logic

SUM, COUT: out std_logic);

end FA;

architecture structural of FA is

component HA is

port (A,B : in std_logic;

S,C : out std_logic););

end component;

component OR2 is

port (P,Q : in std_logic;

R : out std_logic););

end component;

signal TEMP1, TEMP2, TEMP3:std_logic;

begin

HA1 : HA port map (A=>X, B=>Y, S=>TEMP2, C=>TEMP1);

HA2 : HA port map (A=>TEMP2, B=>CIN, S=>SUM, C=>TEMP3);

OR1 : OR2 port map (P=>TEMP1, Q=>TEMP3, R=>COUT);

end structural;