Full Scan:

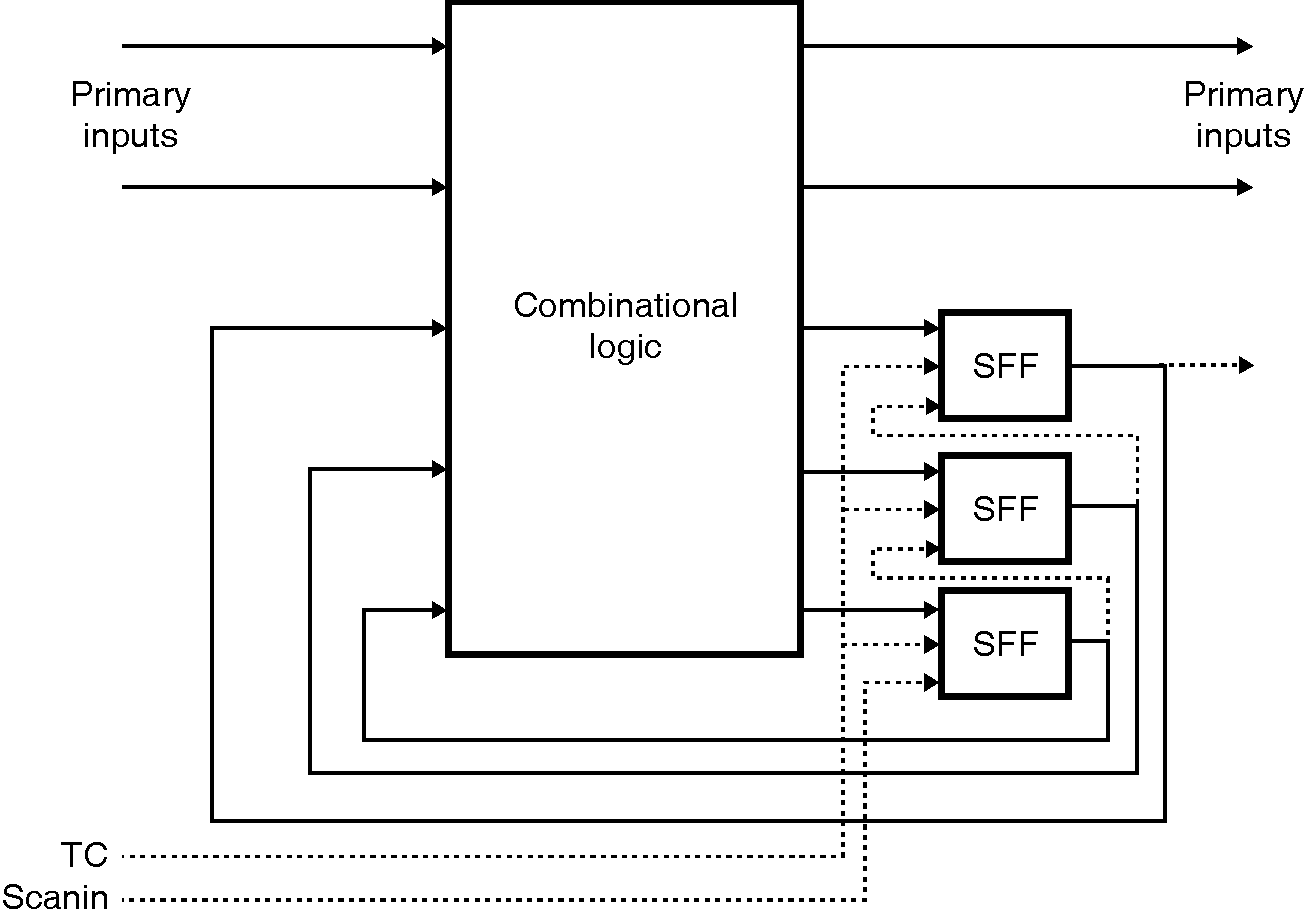

The importance of full scan lies in high-fault coverage for structural defects. Full scan testing of scan circuits is carried out in two phases. The first phase tests the scan register by a shift test. The shift test is used in both single-clock and two-clock designs. On the other hand in second phase, stuck-at faults in the combinational logic are considered and a program is used to generate the test vectors. Further, combinational test vectors are converted into scan sequences and applied to the circuit. The expected output response at primary outputs is specified at clock. Figure below shows full scan testing.

Advantages of full scan :

- The full-scan provides total controllability and observability.

- The full scan lies in the fact that high-fault coverage for structural defects is relatively easy to obtain.

- The test vectors are generated in a predictable amount of time, and there is some control over the size of the test program.

- The test generation time is very small for the full-scan design.

Disadvantages of full scan :

- In full scan some designs are limited by area and performance necessities and some circuitry can not be tested by using scan.

- Further, the presence of Multiple clock domains is the challenge in full scan.

- Another problem with full scan is the length of sequence in full scan larger than the length of sequence in partial-scan.