Partial Scan:

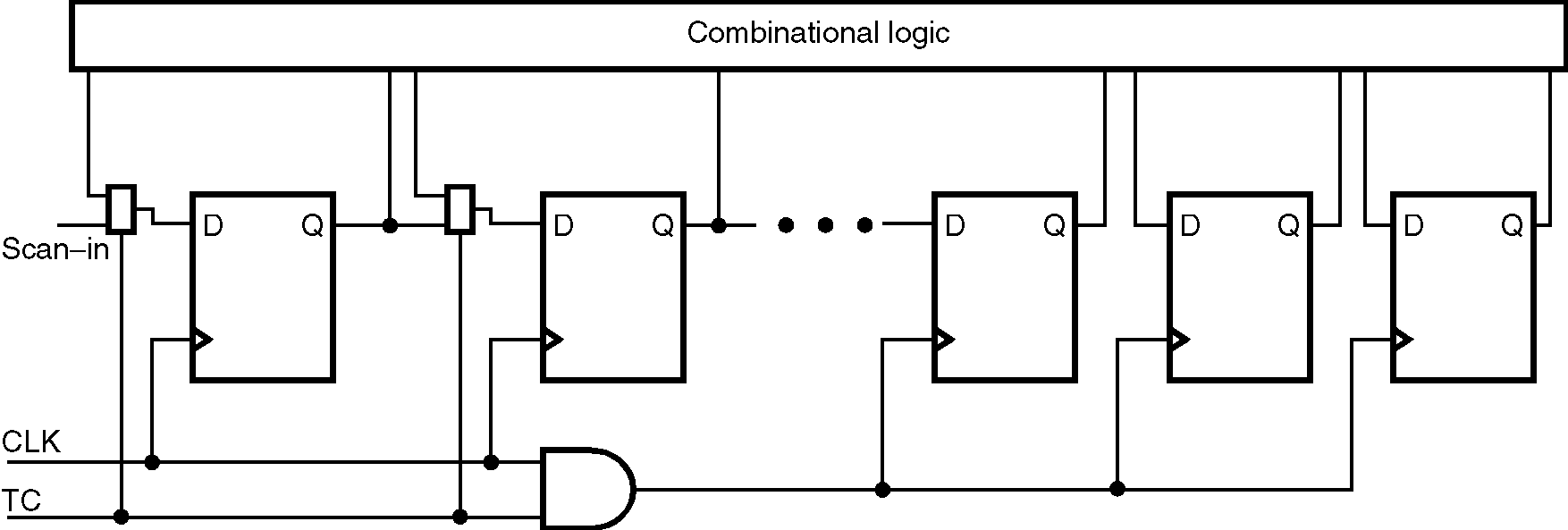

Partial scan is mainly used to test the circuit in which some of the flip-flops are stitched into a scan path. The partial scan chain includes flip-flops from status registers, counters, and state machines. A drawback to partial-scan is if a complete scan-path exists, automatic test pattern generation is simplified and there is no need for an automatic test pattern generation for sequential test patterns. The benefits of partial scan are, if the automatic test pattern generation handle latches, combinational loops, and loop-free sequential logic it is possible to achieve acceptable fault coverage. Figure below shows the partial scan in which the values in the flip-flops on the right side of the circuit are fixed when the test control is 0, whereas the partial scan flip-flops on the left side are loaded by means of the scan-in input.

Advantages of partial scan:

- The gate overhead is significantly lower for partial-scan.

- Partial scan designs improve the fault coverage and fault efficiency to adequately high levels.

Disadvantages of partial scan:

- The test generation time is very small for the full-scan and it is two orders of magnitude higher in partial-scan.

- The scan test sequences are very long due to the scan-in and scan-out operations.

- It requires the use of a sequential automatic test pattern generation program.