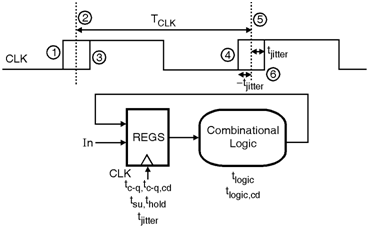

Clock jitter is defined as the temporal variation in clock period of the clock waveform. Due to Clock jitter the clock period of the clock can be reduced or increased. The Clock jitter shows the temporal uncertainty in the semiconductor integrated circuit. In order to measure the clock Jitter various techniques are used. The clock Jitter is mainly the time varying deviation of the single clock period. For a spatial location x clock jitter is given as Tjitter, x(n) = Tx, n+1 - Tx,n - TCLK, where Tx,n is the clock period for period n, Tx, n+1 is clock period for period n+1, and TCLK is the nominal clock period. The presence of clock Jitter in an integrated circuit reduces the performance of sequential digital integrated circuits. Figure below shows the clock period variations due to clock jitter. Here, the clock period starts at edge 2 and ends at edge 5 with a clock period of TCLK. Therefore, the total time to complete the operation given by,

Fig_Clock Jitter