Home > VHDL > Introduction > Synthesis

Synthesis :

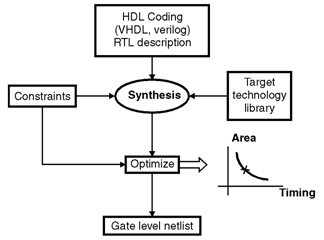

Synthesis is the process of compilation of HDL code. Figure below shows the synthesis process.

RTL description :

In this case the circuit engineer writes the code using VHDL called as RTL code. The designer spends time in functional verification checks the functions correctly. After the functionality is checked the RTL description is input to the logic synthesis tool.

Translation :

The RTL description is converted by the logic synthesis tool. This process is called translation. Translation is relatively simple and uses techniques of HDL constructs interpretation.

Logic optimisation :

The logic is now optimized to remove redundant logic. Various technology independent Boolean logic optimization techniques are used. This process is called logic optimization.

Technology mapping and optimisation :

In this step the synthesis tool takes the internal representation and implements the representation in gates using the cells provided in the library. In other words the design is mapped to the desired target technology.

Technology library :

The technology library contains library cells. It is also called as standard cell library. The term technology library and standard cell library are identical.

Optimized gate level description :

After technology mapping is complete, an optimized gate level netlist described in terms of target technology components is produced