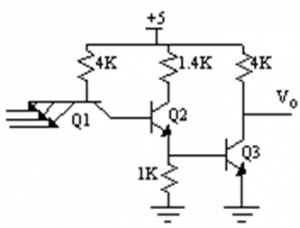

The evolution from Diode transistor Logic to transistor transistor Logic can be seen by observing the placement of p-n junctions. For example, the diode in the DTL can be replaced by a transistor whose collector is pulled up to the power supply. The p-n junction of diode is replaced by the BE junction of transistor and with the current gain of the transistor, the current going into the base of transistor is greatly increased, increasing the fanout. The input diodes are replaced by the multi-emitter NPN transistor. Later on, we will make additional modifications to this circuit to improve its performance further. The analysis of this circuit follows very much the same path as the analysis of the DTL gate. For the most part, we will consider the input transistor, act just like two diodes.

TTL inputs: multiple-emitter

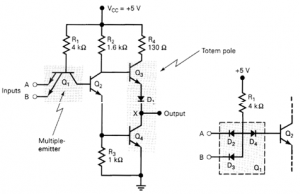

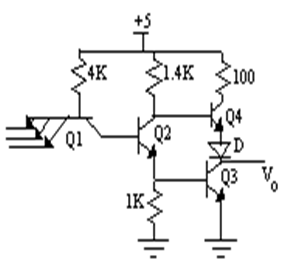

A two input standard TTL NAND gate is a multiple emitter transistor for the inputs A and B. the output transistors Q3 and Q4 form a totem-pole output arrangement.

Operation:

If A or B is low, the base-emitter junction of Q1 is forward biased and its base-collector junction is reverse biased. Then there is a current from Vcc through R1 ti the base emitter junction of Q1 and into the LOW input, which provides a path to the ground for the current. Hence there is no current into the base of Q2 and making it into cur-off. The collector of Q2 is HIGH and turns Q3 into saturation. Since Q3 acts as a emitter follower, by providing a low impedance path from Vcc to the output, making the output into HIGH. At the same time, the emitter of Q2 is at ground potential, keeping Q4 OFF.

When A and B are high, the two input base emitter junctions of Q1 are reverse biased and its base collector junction is forward biased. This permits current through R1 and the base collector junction of Q1 into the base of Q2, thus driving Q2 into saturation. As a result Q4 is turned ON by Q2, and producing LOW output which is near ground potential. At the same time, the collector of Q2 is sufficiently at LOW voltage level to keep Q3 OFF.

TTL outputs: Totem pole/ active pull-up

It is possible in TTL gates the charging of output capacitance without corresponding increase in power dissipation with the help of an output circuit arrangement referred to as an active pull-up or totem-pole output. In this case,

• Outputs must never be connected together.

• Connecting outputs causes excessively high currents to flow.

• Outputs will eventually be damaged.

• The standard TTL output configuration with a HIGH output and a LOW output transistor, only one of which is active at any time.

• A phase splitter transistor controls which transistor is active.

One of the problems with the TTL gate circuit is that the pull-up resistor on the output transistor will prevent rapid charging of any wiring capacitance on the output. One way to improve the rise time is to reduce the resistance value as is often done, but this also increases the power dissipation when the output is low. If we look at the circuit, we observe that when the transistor is saturated, it presents a very low effective resistance to ground. The problem arises when the output is high and the pull-up resistor is too large. Ideally we would like to have a very low resistance pull-up when the output is high, but a very high pull-up resistance when the output is low. In this way, we could get quick charging and very low power dissipation. The totem-pole output stage for TTL, shown in Figure .

The TTL family includes,

standard TTL designed as 74 or 54

low-power TTL designed as 74L or 54L

high-power TTL designed as 74H or 54H

low-power Schottky TTL designed as 74LS or 54LS

Schottky TTL designed as 74S or 54S

advanced low-power Schottky TTL designed as 74ALS or 54ALS

advanced Schottky TTL designed as 74AS or 54AS

Fast TTL designed as 74F or 54F

An alphabetic code preceding this indicates the name of the manufacturer. A two-, three- or four-digit numerical code indicates the logic function performed by the IC.

QUIZ