Home > finite state machines > Metastability > Metastability Synchronizer

Metastability Synchronizer

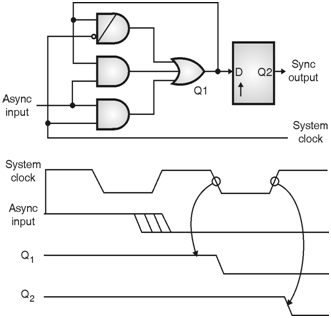

Although circuits show extremely quick metastable settling time, the dsigner has to still improve the MTBF by using its unique internal feedback configuration. Fig. 4.5.3 shows a gated-latch which internally latches the asynchronous input on the falling edge of the system clock and generats the signal Q1. The input with Q1 through the internal feedback path eliminates a possible hazard condition during the clock's high-to- low transitions. Thus, the latch holds Q1 stable to assure the setup-time requirement of the subsequent flip-flop and accepts data on the next rising system clock edge. Similar to two stage synchronizer, the probability that a data goes metastable is the multiplication of two probabilities of each synchronizer. Therefore since the probability of failure becomes small, the MTBF of digital devices improves. While using the measurement setup above, the designer get k1 = 3x1046 and k2 = 0.05 ns with a gated latch.